PL 读写 PS 端 DDR 数据

PL 读写 PS 端 DDR 数据

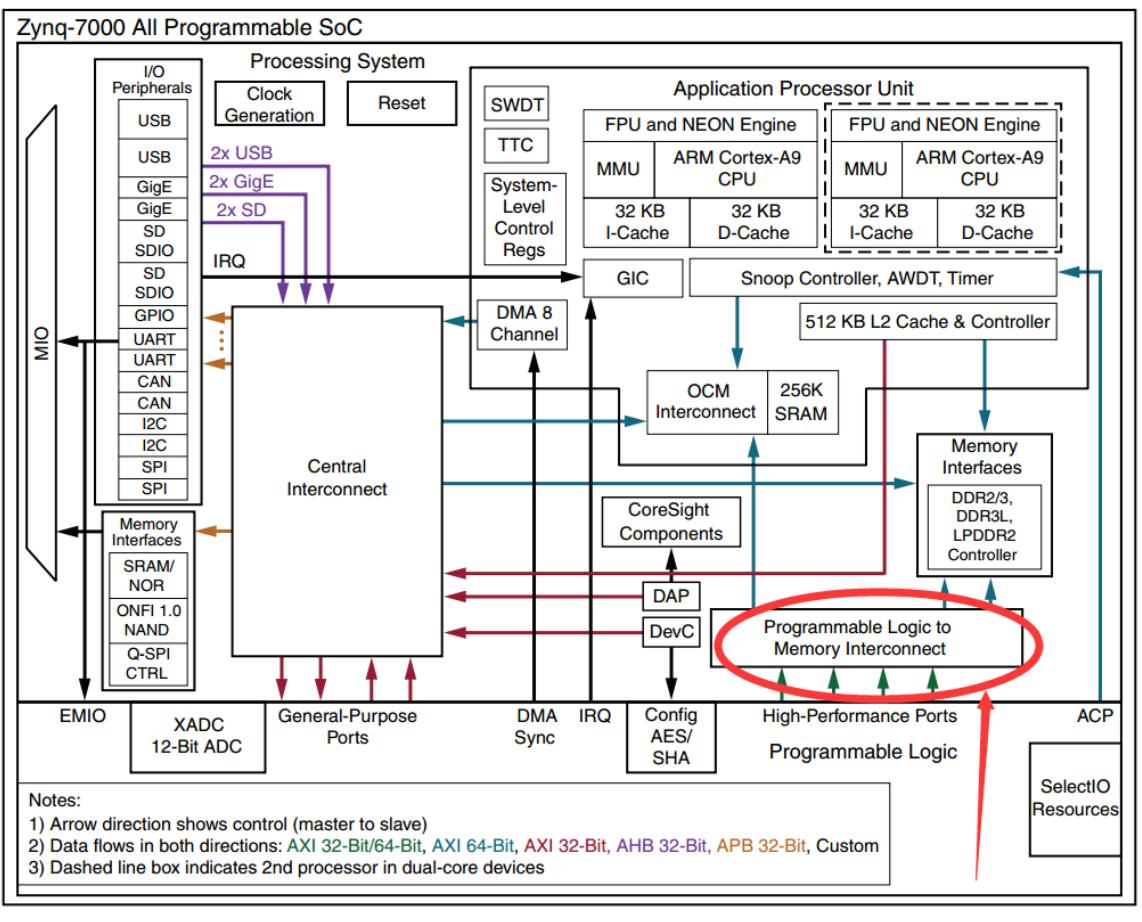

PL 与 PS 之间的高效数据交互是 Zynq-7000 SoC 开发的核心需求之一。常见场景包括将大量在 PL 端采集或处理的数据实时传输至 PS 端进行进一步处理,或将 PS 端的处理结果实时回传至 PL 端用于后续加速。虽然 DMA 是常用方案,但在某些场景下通过 AXI 总线直接访问 DDR 更为直接与灵活。本实验通过 PL 侧 AXI Master 访问 PS 侧 DDR 的实现思路、AXI 协议要点以及 Vivado/SKD 调试技巧。

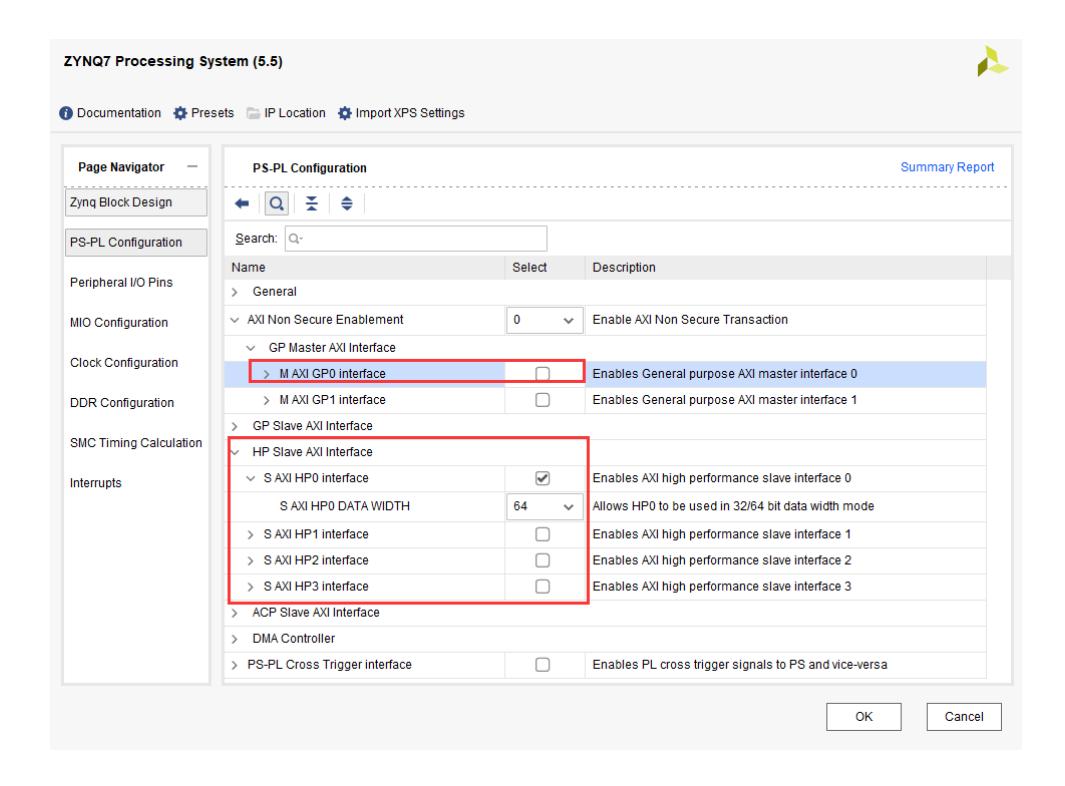

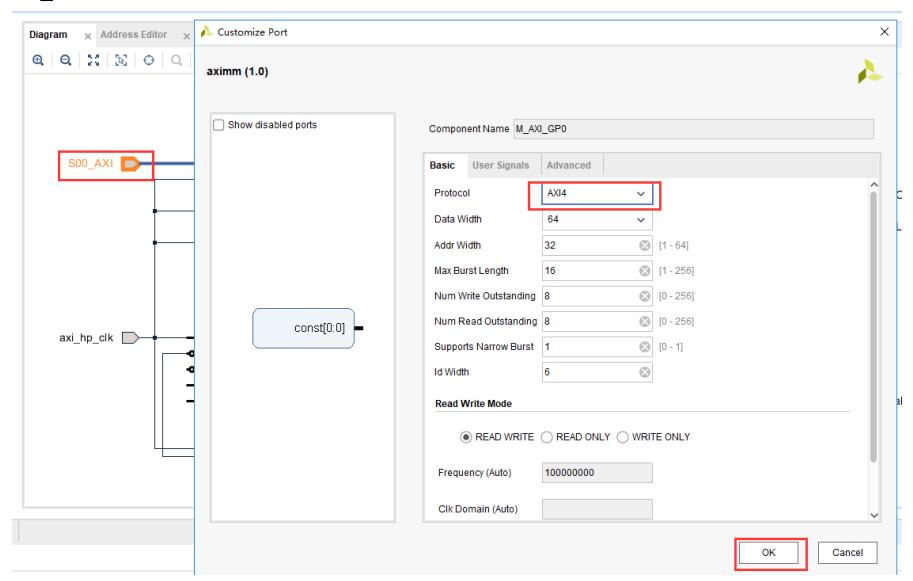

HP 端口与工程配置

Zynq-7000 的 HP(High-Performance)端口提供高带宽的从属接口,常用于 PL 向 PS DDR 发起高吞吐的读写访问。器件通常提供多个 HP 端口(例如 4 个),每个端口可配置数据位宽(例如 32/64 位)与时钟频率,以满足不同应用的带宽需求。在 Vivado 工程中应按如下思路配置 HP 端口:在 Zynq PS 配置中启用所需 HP 端口并设定数据位宽与时钟;若 HP 端口原生遵循 AXI3 协议而设计需要使用 AXI4,则可插入 AXI Interconnect 或协议转换 IP 以完成 AXI3↔AXI4 的互通;将相关时钟(例如 FCLK_CLK0)导出为 PL 时钟源,并在设计中创建相应的复位与时钟域资源;在 S_AXI_HP 接口上设置合适的突发(burst)长度与时序参数,以提高总线利用率与性能。完成上述配置后,建议在 Address Editor 中执行自动地址分配,并进行设计检查与生成输出文件(Generate Output Products),以确保资源与地址映射正确。

AXI4 协议要点

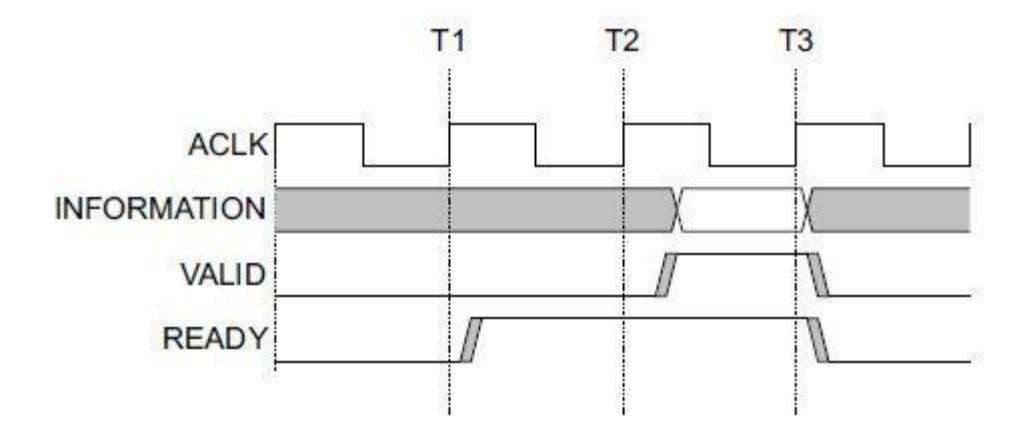

AXI4 采用 VALID/READY 握手机制,通道分为五类:读地址通道、写地址通道、读数据通道、写数据通道与写响应通道。每个通道通过各自的 VALID 与 READY 信号完成握手并传递地址、数据与响应信息。关键要点包括:AR/AW 通道传输地址信息并进行握手;W 通道传输写数据并通过 WSTRB 表示有效字节;R 通道返回读数据与读响应(RRESP),B 通道返回写响应(BRESP);ACLK 为总线时钟,ARESETN 为低有效复位。在设计 AXI Master 时,必须严格实现每一通道的握手逻辑并处理好突发传输(burst)与对齐问题。详尽规范请参考 Xilinx 的 UG761 AXI 参考指南。

在 PL 实现 AXI Master 的方法与功能

实现 PL 侧 AXI Master 的常见实现方法与其主要功能应以工程需求为导向。可采用现成的 AXI Master IP(如 Xilinx 提供的 DMA/VDMA 等),这些 IP 的主要功能是提供成熟的总线协议支持、高吞吐数据搬运能力与驱动支持,适用于大数据流场景;在无法直接使用现成 IP 时,可以参考并裁剪社区或开源的 AXI Master 实现(例如 aq_axi_master),将其作为参考实现以快速构建自定义读写逻辑,此类方法的功能是允许灵活定制握手、突发与缓存策略以适配特殊需求;当选择自行实现时需特别注意地址单位(AXI 地址为字节单位)、对齐与事务边界,以及 DDR 地址空间与 PS 端 DDR 控制器的起始地址与大小,确保所生成的事务在目标控制器地址映射范围内工作。测试阶段通常实现一个简单的内存写入/读取验证模块(例如 mem_test),通过向 DDR 指定地址写入已知模式数据并读回比较,以判定读写正确性并定位对齐或突发相关问题。

调试工具与方法

为便于定位 AXI 事务与数据错误,可使用 Vivado 的片上逻辑分析工具(ILA)与 Hardware Manager 的 Logic Analyzer:在设计中添加 ILA(或通过 Set Up Debug 向导生成调试核),并将关键信号(如 AWVALID/ARVALID/WVALID/WDATA/RDATA/BRESP 等)连接至 ILA;在生成比特流后,通过 Hardware Manager 的 Logic Analyzer 捕获并查看时序波形,判断握手时序、突发传输是否正常与数据完整性;若验证模块仅报告 error 信号,可将该 error 信号映射到 LED 或在 ILA 中捕获更多上下文信号以便定位错误来源。上述方法在排查 AXI 时序、突发长度与地址对齐问题时尤为有效。

验证流程与运行步骤

验证示例的一般流程为:在 Vivado 中生成比特流并导出硬件平台;在 SDK 中创建最小的应用(例如一个简单的 HelloWorld),该程序仅用于启动 PS 并确保 DDR 控制器处于工作状态;在 SDK 中下载固件(包括 FSBL、必要的比特流支持与应用),并启动系统;使用 Vivado 的 Hardware Manager 连接目标并启动 Logic Analyzer 捕获数据帧,观察读写事务与验证模块的 error 输出,确认 DDR 读写成功或定位问题。在具体实验中,捕获到的波形若显示读写请求与响应正常且 error 保持为低,则可认为 PL 至 PS DDR 的读写验证通过,用户可进一步检查写入 DDR 的数据与读出数据以确认数据一致性。

数据正常后,用户可以自行在 ILA 波形中查看相关信号以验证写入与读取的数据内容。

教学性总结与能力目标

PL 与 PS 之间的高效协作要求对 AXI 协议、Zynq 的互联资源以及 Vivado/SDK 的调试工具有扎实理解。通过本章实践,读者应掌握以下能力:在 Vivado 中正确配置 HP 端口及其时钟/复位域;理解并实现 AXI4 的握手与突发传输机制;在 PL 中实现或集成 AXI Master 以访问 PS DDR,并设计简单的读写验证逻辑;使用 ILA 与 Hardware Manager 进行时序捕捉与问题定位。掌握这些能力有助于构建高性能异构系统,建议结合官方文档(如 UG761、UG585 等)深入学习并在实际项目中反复练习。